network on chip (NoC)

The miniaturization of devices and the ever-increasing degree of integration of chips have led to entire systems with processors, controllers, memory chips and other components being housed on one chip. This stage of development is formed by system-on-chips( SoC), which is characterized by internal bus architectures and via which the individual components communicate with each other.

Bus technology can only support a limited number of components sufficiently efficiently and also has unpredictable behavior for the individual components, since many other components use the internal bus. For the above reasons and others related to physics, architecture, and operating system, the development of network-on-chips (NoC) was advanced in the 1990s.

The term network-on-chip encompasses the hardware infrastructure, middleware, communication services and operating system, design technologies, and application mapping on the NoC platform. NoCs support multiple asynchronous clock pulses, they combine network theory with systematic networking methods to provide on-chip communications, they improve scalability, and they result in significant performance improvement over system-on-chips.

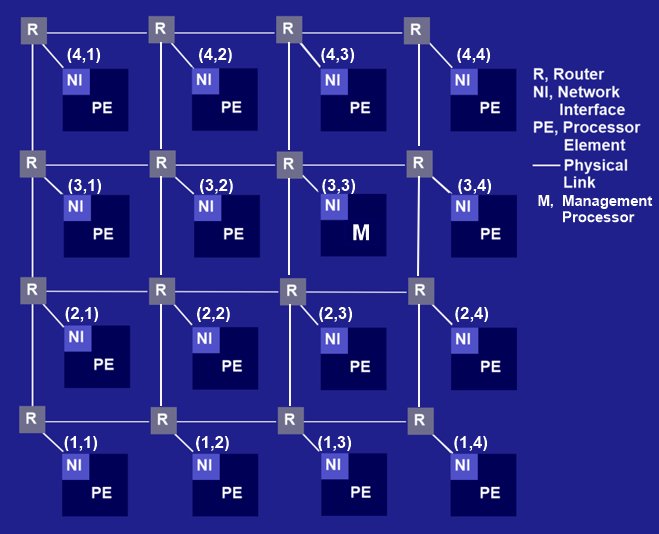

NOCs usually have a meshed structure and consists of a matrix of processors and management components interconnected in rows and columns. As for the processors, they are a wide variety of processors. They can be video transmitters and video receivers, digitalsignal processors( DSP), audio transmitters and audio receivers, FPGAs, memories or other components equipped with processors.

Routers are located at the intersections of the connections. Unlike system-on-chips, the individual processors, memories, controllers and other components do not exchange their information via an internal bus, but via layered bus architectures, via networks and routers, using data packet switching. Whereby the information on the way from the source component to the receiving component can be switched as point-to-point connection or multi-point connection over several links. And, as with a network, by means of routing. The data rates and data throughput are many times higher than those of bus systems. Throughput rates of over 100 GB/s can be achieved with NoC systems.

The NoC architecture

In principle, a network-on-chip is comparable to a network with switching or data packet switching via multiplexed links.

The NoC architecture consists of several layers: the physical layer, transport layer, transaction layer and application layer. The physical layer provides the electrical infrastructure with its signal lines. It determines how data packets are transmitted over the physical medium and interfaces. The transport layer determines the rules for routing the information, taking the applications into account. The data packet format used is extremely flexible and can be adapted to the requirements of the transaction layer. This layer supports transaction services and defines the information exchange. The application layer passes the data to the network interfaces for the LAN and WAN connections.

In general, the network of a Network on Chip can have any topology. This can be a bus topology, star topology, ring topology, tree top ology, or an efficient, fault-tolerant Butterfly Fat Tree( BFT). However, these topologies have certain limitations in terms of data rate and because of the many intersecting links. Therefore, a meshed topology is often used. Such a topology consists of an array of different processors, each of which has its own network interface and router. Corresponding arrays can be designed as 3D chips layered on top of each other. Another topology is the efficient, fault-tolerant Butterfly Fat Tree (BFT).