scalable processor architecture (SPARC)

The Scalable Processor Architecture (SPARC) stands for a microprocessor architecture developed by Sun Labs and is the namesake for a workstation generation.

The development of the SPARC processors

In 1987 with SPARC a 32-bit processor in RISC architecture was introduced, which was characterized by a high computing power. Compared to the Intel processors 80386 and 80486, the first SPARC had only 55,000 transistors although a floating point unit( FPU), the memory manager( MMU) and a level 1 cache were integrated on the chip. The organization of the many 32-bit registers, depending on the version there can be between 40 and 520, is much more efficient in contrast to the competitors.

The SPARC has a high computing power and works exclusively with 32 bit wide instructions. The average execution time for the first SPARC was 1.3 clocks, in contrast to the 80386, which required 4.4 clocks.

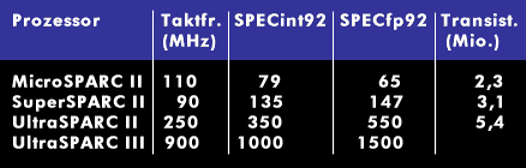

The different SPARC versions that exist are called MicroSPARC, SuperSPARC and UltraSPARC.

The MicroSPARC, which consists of 2.3 million transistors, is a low-cost version of a 32-bit Risc processor with a clock rate of 110 MHz. It has 136 32-bit registers, integrated level 1 cache with for code and data with 16 KB and 8 KB respectively, integrated floating point unit (FPU), S-Bus interface and DRAM controller.

The UltraSPARC-II is a powerful 64-bit processor whose clock speed was increased from 250 MHz in 1997, to 360 MHz in 1998, to 450 MHz in 1999. In version III, an increase to 900 MHz follows in 2000 and finally to 1.05 GHz in 2002. In the UltraSPARC, 3 floating point units (FPU) and 2 graphics units are integrated and the Visual Instruction Set (VIS) is used to support multimedia capabilities. Further development shows the SPARC 64V in 130 nm technology with a clock frequency of 1.35 GHz in 2003, followed by the SPARC 64V+ in 90 nm technology and 1.89 GHz, whose clock rate is increased to 2.16 GHz in 2005. Then in 2007 and 2008 comes the dual-core processor for multithreading, the SPARC VI with 2.4 GHz, which consists of two UltraSPARC III cores, and in 2008 the quad-core processor SPARC VI+ in 65-nm technology and 2.7 GHz.

In 2012, the SPARC64X, a high- performance server processor with a clock frequency of 3GHz, was developed. It is a multi-core processor with 16 cores and an L2 cache of 24 MB. The software functions are accelerated by integrated hardware components. The theoretical computing power is 382 GFLOPS, and the memory bandwidth is 102 GB/s.

The SPARC63X is manufactured in 28 nm technology.