Die Verkleinerung der Geräte und der ständig steigende Integrationsgrad von Chips haben dazu geführt, dass ganze Systeme mit Prozessoren, Controllern, Speicherbausteinen und anderen Komponenten auf einem Chip untergebracht sind. Diese Entwicklungsstufe bilden die System-on-Chips ( SoC), die durch interne Bus- Architekturen geprägt ist und über die die einzelnen Komponenten miteinander kommunizieren.

Die Bus-Technologie kann nur eine begrenzte Anzahl an Komponenten hinreichend effizient unterstützen und hat zudem für die einzelnen Komponenten ein nicht vorhersagbares Verhalten, da viele andere Komponenten den internen Bus nutzen. Aus den genannten und weiteren Gründen, die in der Physik, der Architektur und dem Betriebssystem liegen, wurde in den 90er Jahren die Entwicklung der Network-on-Chips (NoC) vorangetrieben.

Die Bezeichnung Network-on-Chip umfasst die Hardware- Infrastruktur, die Middleware, Kommunikationsservices und das Betriebssystem, die Design-Technologien und die Abbildung von Anwendungen auf der NoC- Plattform. NoCs unterstützen mehrere asynchrone Taktimpulse, sie kombinieren die Netzwerktheorie mit systematischen Netzwerkmethoden zu einer On-Chip- Kommunikation, sie verbessern die Skalierbarkeit und führen zu einer wesentlichen Leistungsverbesserung gegenüber den System-on-Chips.

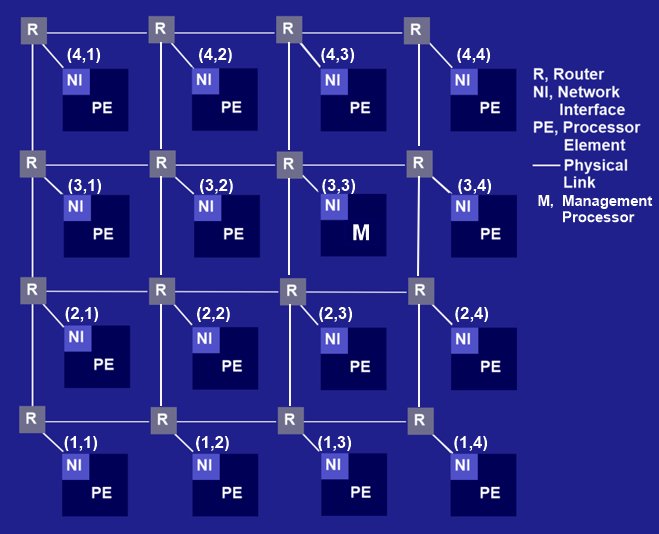

NOCs haben meistens eine vermaschte Struktur und besteht aus einer Matrix aus Prozessoren und Management-Komponenten, die zeilen- und spaltenmäßig miteinander verbunden sind. Was die Prozessoren betrifft, so handelt es sich um unterschiedlichste Prozessoren. Das können Video Transmitter und Video Receiver sein, Digital Signal Processor ( DSP), Audio Transmitter und Audio Receiver, FPGAs, Speicher oder andere mit Prozessoren ausgestattete Komponenten handeln.

An den Kreuzungspunkten der Verbindungen befinden sich Router. Im Unterschied zu System-on-Chips tauschen die einzelnen Prozessoren, Speicher, Controller und andere Komponenten ihre Informationen nicht über einen internen Bus, sondern über geschichtete Bus-Architekturen, über Netzwerke und Router, und zwar mittels Datenpaketvermittlung. Wobei die Informationen auf dem Weg von der Quellkomponente zur Empfangskomponente als Punkt-zu-Punkt-Verbindung oder Mehrpunktverbindung über mehrere Links geschaltet werden kann. Und zwar, wie bei einem Netzwerk, mittels Routing. Die Datenraten und der Datendurchsatz sind dabei um ein Vielfaches höher als der von Bussystemen. Mit NoC-Systemen können Durchsatzraten von über 100 GB/s erreicht werden.

Die NoC-Architektur

Prinzipiell ist ein Network-on-Chip vergleichbar einem Netzwerk mit Switching oder Datenpaketvermittlung über gemultiplexte Links.

Die NoC-Architektur besteht aus mehreren Schichten: der physikalischen Schicht, Transportschicht, Transaktionsschicht und Anwendungsschicht. Die physikalische Schicht stellt die elektrische Infrastruktur mit ihren Signalleitungen. Sie bestimmt wie die Datenpakete über das physikalische Medium und die Schnittstellen übertragen werden. Die Transportschicht bestimmt die Regeln für das Routing der Informationen unter Berücksichtigung der Anwendungen. Das benutzte Datenpaketformat ist dabei äußerst flexibel und kann sich an die Anforderungen der Transaktionsschicht anpassen. Diese Schicht unterstützt Transaktionsdienste und definiert den Informationsaustausch. Die Anwendungsschicht übergibt die Daten an die Netzwerkschnittstellen für die LAN- und WAN-Anbindungen.

Generell kann das Netzwerk eines Network on Chip eine beliebige Topologie haben. Das kann eine Bustopologie, Sterntopologie, Ringtopologie, Baumtopologie sein oder ein effizienter, fehlertoleranter Butterfly Fat Tree ( BFT). Allerdings haben diese Topologien gewisse Einschränkungen in Bezug auf die Datenrate und wegen der vielen sich überschneidenden Verbindungen. Deswegen wird häufig mit einer Meshed Topology gearbeitet. Eine solche Topologie besteht aus einem Array aus verschiedensten Prozessoren, von denen jeder für sich ein Network Interface und einen Router hat. Entsprechende Arrays können als 3D-Chips lagenmäßig übereinander ausgeführt sein. Eine weitere Topologie ist der effiziente, fehlertolerante Butterfly Fat Tree (BFT).